Advancing chip fundamentals through material and thermal innovation.

CoolSem’s patented wafer-level thermal management technology helps chips run cooler, last longer, and perform beyond today’s limits.

CoolSem’s patented wafer-level thermal management technology helps chips run cooler, last longer, and perform beyond today’s limits.

Scroll to discover

Learn more about our mission

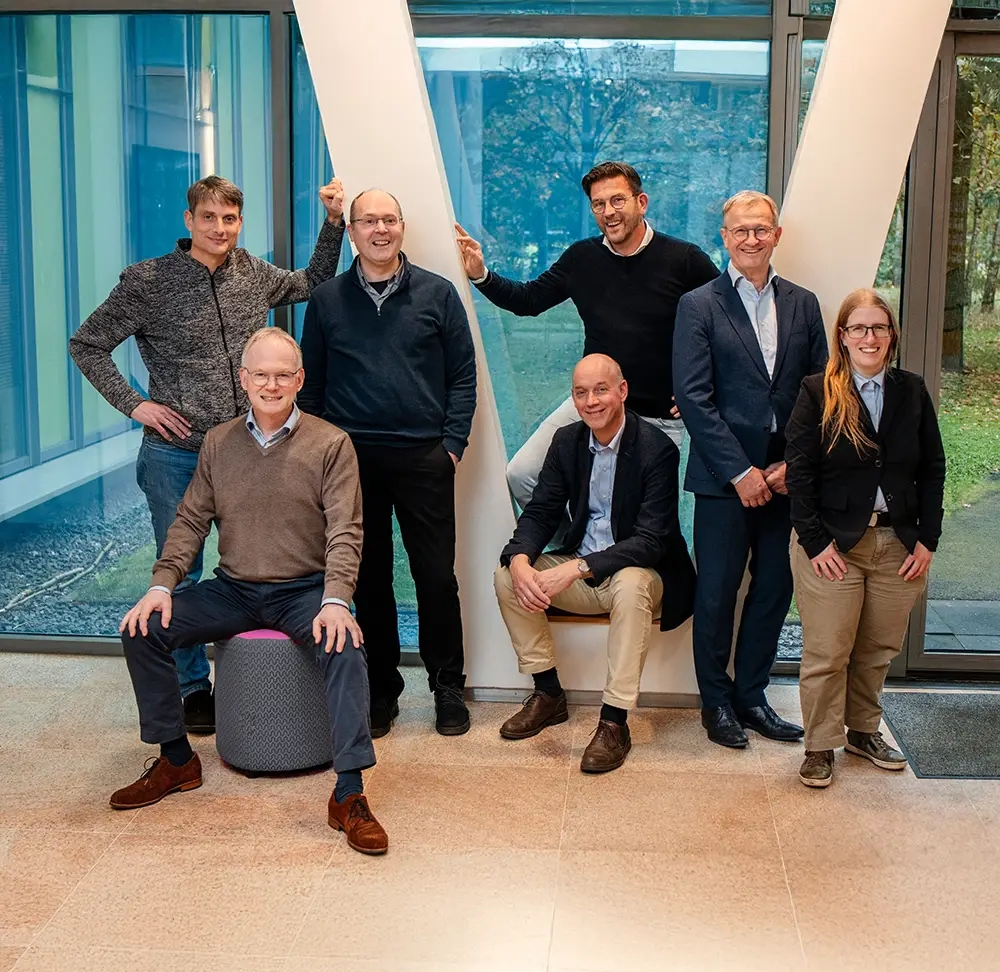

We redefine semiconductor performance through material and thermal innovation.

Watch how our team works on this mission

why heat limits chips

While traditional cooling techniques remove heat from the package or system level, the real challenge lies deeper.

In the thermal resistance of the chip’s substrate.

Active device

Substrate

heatsink

But the challenge goes deeper than heat itself.

As devices cycle through temperature changes, the different materials inside each chip expand and contract at different rates — adding mechanical stress on top of thermal resistance. Over time, this stress degrades interfaces and compounds the very heat problem it’s meant to control.

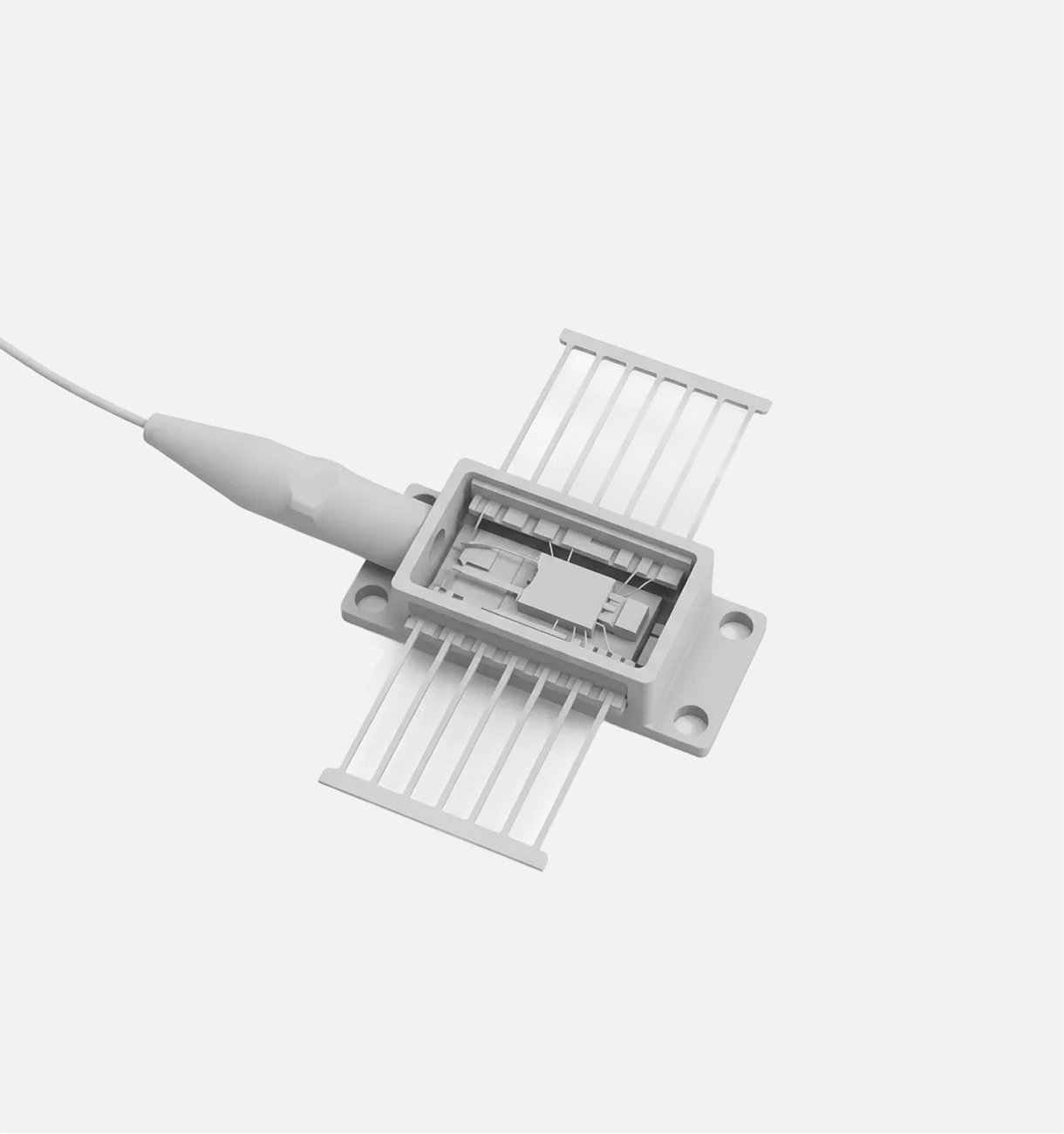

Our wafer based solution

CoolSem removes the substrate, the barrier to efficient heat flow.

And we replace it with our patented wafer-level carrier that conducts heat up to 15× better.

Active Devices

Substrate

Waltis ®

15× better thermal pathway, zero layout constraints

Our patented WaLTIS® wafer-level technology reduces thermal resistance by up to 15× and eliminates hotspots that degrade device performance and reliability. At the same time, the architecture remains dielectrically neutral — fully compatible with existing device layouts and electrical isolation schemes.

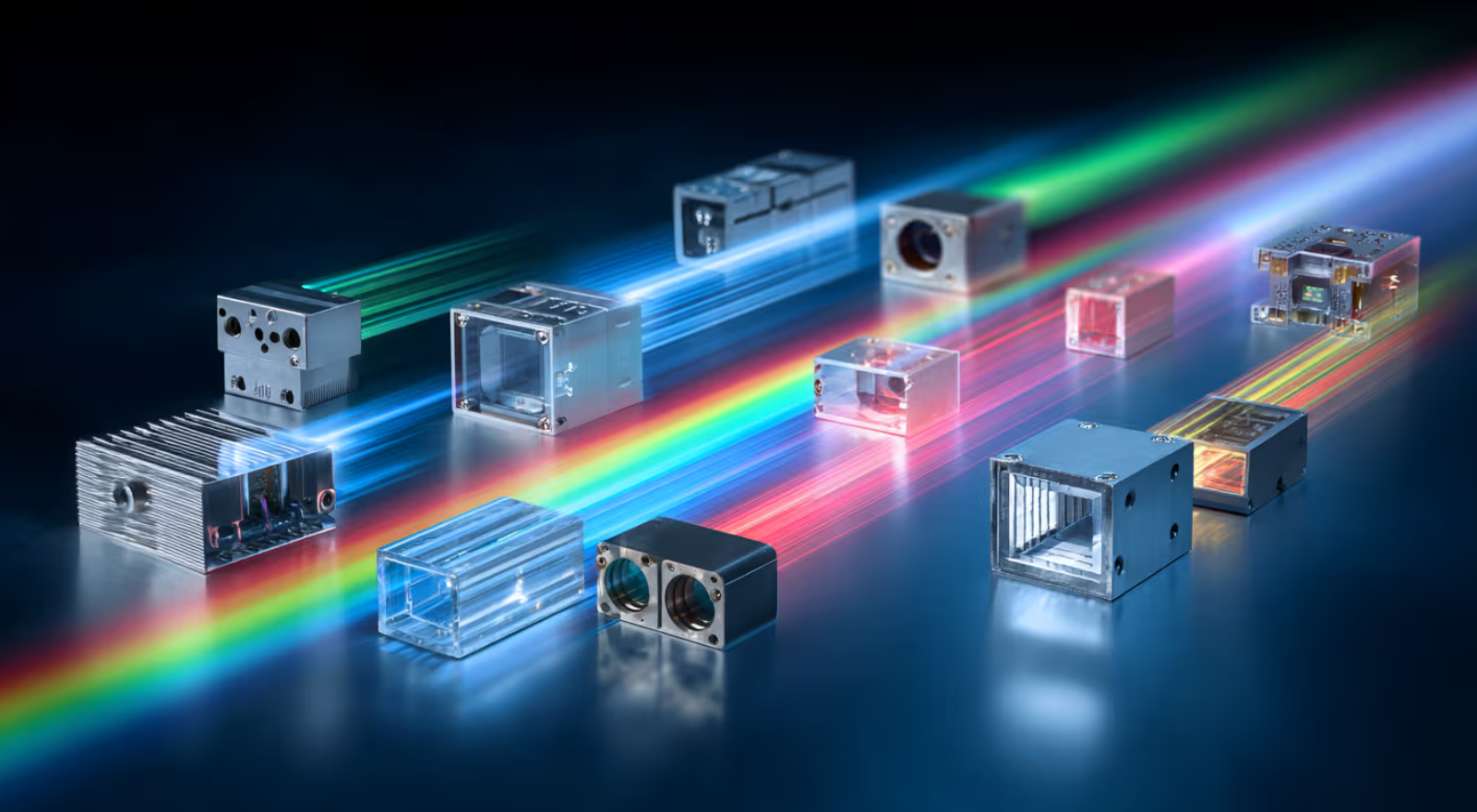

Key application domains

Engineered substrate for hotspot relief

WaLTIS directly targets the die-to-substrate bottleneck, lowering junction temperature and smoothing mechanical stress where GaN, GaAs, InP and SiC devices run hottest.

Front-end neutral, Back-end friendly integration

WaLTIS integrates after device fabrication, preserving existing SiC/GaN wafer lines while fitting seamlessly into today’s die-attach, DBC, and module assembly flows.

Flexible Across Platforms and Process Flows

WaLTIS integrates with varied device types and manufacturing routes, enabling high-performance substrates without altering upstream designs or downstream assembly.